《數(shù)字集成電路 電路、系統(tǒng)與設(shè)計(jì)》第二版中的軟件開發(fā)角色

《數(shù)字集成電路:電路、系統(tǒng)與設(shè)計(jì)》(第二版)是一本廣泛使用的經(jīng)典教材,深入探討了數(shù)字集成電路從物理基礎(chǔ)到系統(tǒng)設(shè)計(jì)的全流程。在當(dāng)今高度自動化的芯片設(shè)計(jì)領(lǐng)域,軟件開發(fā)已不再是輔助工具,而是貫穿整個集成電路設(shè)計(jì)與驗(yàn)證的核心支柱。本書雖以電路與系統(tǒng)理論為主,但其內(nèi)容與軟件開發(fā)實(shí)踐密不可分,主要體現(xiàn)在以下幾個方面:

一、 設(shè)計(jì)自動化與EDA工具鏈

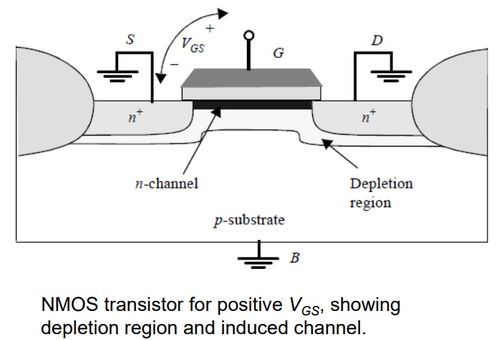

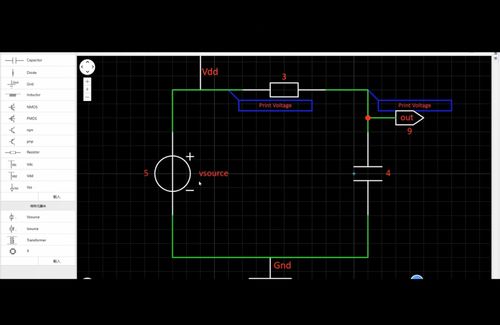

現(xiàn)代數(shù)字集成電路的復(fù)雜度(動輒數(shù)十億晶體管)已遠(yuǎn)非手工設(shè)計(jì)所能應(yīng)對。因此,本書涉及的幾乎所有設(shè)計(jì)階段——從寄存器傳輸級(RTL)描述、邏輯綜合、物理版圖設(shè)計(jì)到時序與功耗分析——都依賴于強(qiáng)大的電子設(shè)計(jì)自動化(EDA)軟件。例如,硬件描述語言(如VHDL/Verilog)的編碼、用于綜合的腳本編寫、以及形式驗(yàn)證工具的使用,本質(zhì)上都是軟件開發(fā)活動。工程師必須掌握相關(guān)軟件工具的使用方法和背后的算法原理,才能高效完成設(shè)計(jì)。

二、 硬件描述語言(HDL)與建模

本書重點(diǎn)介紹的硬件描述語言,是硬件設(shè)計(jì)與軟件工程的交叉點(diǎn)。編寫RTL代碼(即用代碼描述電路的功能和結(jié)構(gòu))是數(shù)字設(shè)計(jì)工程師的核心技能。這要求開發(fā)者不僅具備軟件編程的思維(如模塊化、可讀性、可重用性),更需深刻理解代碼如何映射為實(shí)際的硬件電路(時序、面積、功耗)。第二版中對HDL建模技巧和可綜合代碼風(fēng)格的強(qiáng)調(diào),正是軟件開發(fā)實(shí)踐在硬件設(shè)計(jì)中的直接體現(xiàn)。

三、 驗(yàn)證與仿真平臺開發(fā)

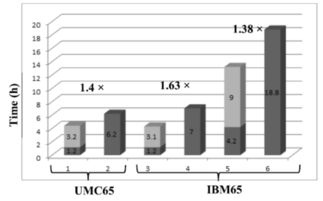

驗(yàn)證是芯片設(shè)計(jì)中最耗時、最依賴軟件的環(huán)節(jié)。書中涉及的驗(yàn)證方法,如測試平臺(Testbench)構(gòu)建、功能仿真、以及斷言檢查,都需要開發(fā)復(fù)雜的軟件程序。這些程序使用HDL或更高級的驗(yàn)證語言(如SystemVerilog/UVM)編寫,用于生成測試激勵、檢查輸出結(jié)果、實(shí)現(xiàn)覆蓋率驅(qū)動驗(yàn)證。構(gòu)建一個高效、可重用的驗(yàn)證環(huán)境,其復(fù)雜度和重要性不亞于開發(fā)一個大型軟件系統(tǒng)。

四、 嵌入式軟件與軟硬件協(xié)同

對于片上系統(tǒng)(SoC)而言,數(shù)字集成電路(硬件)最終需要與運(yùn)行其上的嵌入式軟件(如驅(qū)動程序、操作系統(tǒng)、應(yīng)用程序)協(xié)同工作。本書在系統(tǒng)設(shè)計(jì)層面為理解軟硬件接口(如總線、存儲器映射、中斷機(jī)制)奠定了基礎(chǔ)。軟硬件協(xié)同設(shè)計(jì)與驗(yàn)證,需要開發(fā)者在硬件設(shè)計(jì)早期就考慮軟件的需求和模型,這進(jìn)一步模糊了硬件與軟件的界限。

五、 腳本與流程自動化

實(shí)際的設(shè)計(jì)流程包含大量重復(fù)性任務(wù),如批量仿真、數(shù)據(jù)整理、結(jié)果報告生成等。精通Python、Perl、Tcl等腳本語言,用于編寫自動化腳本以管理設(shè)計(jì)流程和數(shù)據(jù)處理,已成為數(shù)字IC工程師提升效率的關(guān)鍵。這種“開發(fā)工具的工具”的能力,是軟件思維在工程設(shè)計(jì)中的直接應(yīng)用。

《數(shù)字集成電路:電路、系統(tǒng)與設(shè)計(jì)》第二版雖是一本硬件導(dǎo)向的教材,但其描述的現(xiàn)代設(shè)計(jì)范式已與軟件開發(fā)深度融合。掌握相關(guān)的軟件工具、編程語言和自動化技能,對于將書中的電路與系統(tǒng)理論轉(zhuǎn)化為實(shí)際、可靠、高效的芯片產(chǎn)品至關(guān)重要。未來的芯片設(shè)計(jì)工程師,必然是精通硬件原理的“軟件開發(fā)者”。

如若轉(zhuǎn)載,請注明出處:http://www.tpyd.com.cn/product/52.html

更新時間:2026-03-09 10:32:18