研討會精華分享四 以成功率和可靠性為核心的納米尺度集成電路設(shè)計方法學(xué)與軟件開發(fā)

隨著集成電路工藝節(jié)點不斷向納米乃至更小尺度演進(jìn),傳統(tǒng)設(shè)計方法學(xué)正面臨前所未有的挑戰(zhàn)。在近期舉辦的“先進(jìn)集成電路設(shè)計”系列研討會上,第四場專題聚焦于“成功率和可靠性驅(qū)動的納米尺度集成電路設(shè)計方法學(xué)與軟件開發(fā)”,多位業(yè)界專家與學(xué)者分享了前沿洞見與實踐經(jīng)驗。

一、 納米尺度設(shè)計面臨的嚴(yán)峻挑戰(zhàn)

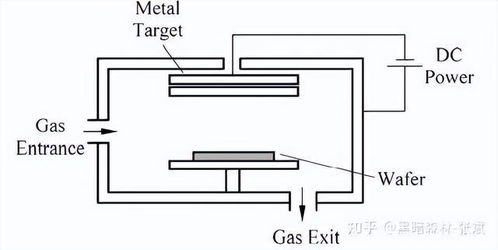

當(dāng)特征尺寸進(jìn)入深納米領(lǐng)域(如7納米、5納米及以下),物理效應(yīng)愈發(fā)顯著。量子隧穿、工藝波動、電遷移、熱效應(yīng)以及更復(fù)雜的互連寄生參數(shù)等問題,使得設(shè)計首次成功率(First-Time Success Rate)急劇下降,芯片的長期可靠性也面臨嚴(yán)峻考驗。單純追求性能與功耗指標(biāo)的傳統(tǒng)設(shè)計流程已難以滿足需求,必須在設(shè)計初期就將制造成功率和長期可靠性作為核心驅(qū)動目標(biāo)。

二、 成功率和可靠性驅(qū)動的設(shè)計方法學(xué)核心

新型方法學(xué)的核心在于將“可制造性設(shè)計”(DFM)和“可靠性設(shè)計”(DFR)理念深度融合,并前置到設(shè)計流程的每一個關(guān)鍵環(huán)節(jié)。

- 預(yù)測與建模先行:建立高精度的工藝與器件波動模型、老化模型(如BTI、HCI)、軟錯誤率模型以及熱模型。這些模型是進(jìn)行早期分析和優(yōu)化的基礎(chǔ)。

- 設(shè)計空間協(xié)同探索:在架構(gòu)設(shè)計、邏輯綜合、物理實現(xiàn)等階段,工具需能夠同時評估性能、功耗、面積(PPA)與良率、可靠性指標(biāo),實現(xiàn)多目標(biāo)協(xié)同優(yōu)化。

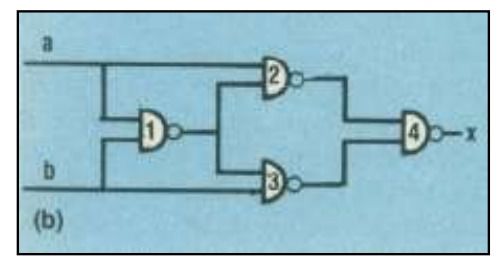

- 冗余與容錯設(shè)計:在系統(tǒng)架構(gòu)層面,明智地引入冗余設(shè)計(如ECC、冗余邏輯單元)和自適應(yīng)調(diào)節(jié)機(jī)制(如動態(tài)電壓頻率調(diào)整DVFS),以容忍部分失效,提升系統(tǒng)級可靠性。

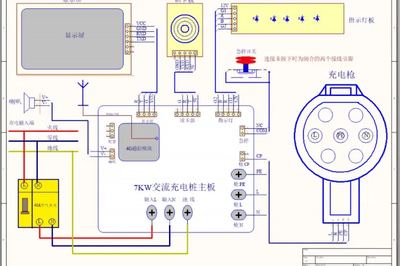

- 簽核流程的強(qiáng)化:除了傳統(tǒng)的時序、功耗簽核外,必須引入并嚴(yán)格執(zhí)行電遷移簽核、熱簽核、可靠性簽核(如老化分析)和制造良率簽核,形成全面的“可靠性簽核”閉環(huán)。

三、 支撐方法學(xué)的關(guān)鍵軟件開發(fā)

先進(jìn)的方法學(xué)離不開強(qiáng)大軟件工具的支撐。相關(guān)軟件開發(fā)呈現(xiàn)以下趨勢:

- 智能化與自動化:利用機(jī)器學(xué)習(xí)(ML)和人工智能(AI)技術(shù),從海量設(shè)計數(shù)據(jù)與制造數(shù)據(jù)中學(xué)習(xí),快速預(yù)測設(shè)計熱點、潛在故障點并自動生成優(yōu)化方案,極大提升設(shè)計效率和成功率。例如,ML驅(qū)動的布局布線、良率預(yù)測和參數(shù)調(diào)優(yōu)。

- 多物理場仿真集成:開發(fā)能夠耦合電路、熱、機(jī)械應(yīng)力等多物理場效應(yīng)的仿真平臺,實現(xiàn)更真實的可靠性評估。

- 全流程數(shù)據(jù)管理與協(xié)同:建立統(tǒng)一的設(shè)計數(shù)據(jù)管理平臺,確保從架構(gòu)到制造的每一環(huán)節(jié)都能獲取一致、準(zhǔn)確的模型與約束信息,實現(xiàn)真正的“左移”(Shift-Left),讓可靠性考量盡早介入。

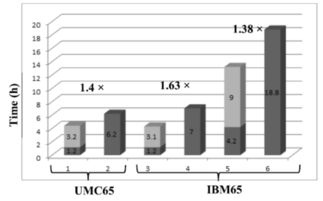

- 云原生與彈性計算:面對日益增長的計算復(fù)雜度(如蒙特卡洛分析、大規(guī)模參數(shù)掃描),設(shè)計工具正轉(zhuǎn)向云原生架構(gòu),利用彈性計算資源并行處理,使原本耗時數(shù)周的分析能在數(shù)小時內(nèi)完成。

四、 未來展望

專家們一致認(rèn)為,面向更先進(jìn)的工藝節(jié)點,成功率和可靠性將不再是設(shè)計流程末端的“檢查項”,而是貫穿始終的“驅(qū)動力”。未來方法學(xué)與軟件的演進(jìn),將更加強(qiáng)調(diào)系統(tǒng)-電路-工藝的協(xié)同優(yōu)化(DTCO),以及借助人工智能實現(xiàn)設(shè)計范式的根本性變革。開源設(shè)計工具與生態(tài)的崛起,也為更多創(chuàng)新者參與這一關(guān)鍵領(lǐng)域提供了可能。

本次研討會清晰地指出,唯有通過方法學(xué)的革新與軟件工具的強(qiáng)力賦能,才能在納米尺度集成電路設(shè)計的復(fù)雜迷宮中,開辟出一條通向高成功率、高可靠性的路徑,支撐起下一代信息技術(shù)的堅實基礎(chǔ)。

如若轉(zhuǎn)載,請注明出處:http://www.tpyd.com.cn/product/63.html

更新時間:2026-03-07 02:39:24