MOS管的輸出電阻rout與溝道長度L在CMOS集成電路仿真設(shè)計(jì)中的關(guān)系及其軟件開發(fā)應(yīng)用

在模擬CMOS集成電路設(shè)計(jì)中,MOS晶體管的輸出電阻(rout)與溝道長度(L)是兩個(gè)關(guān)鍵參數(shù),它們直接影響電路性能,如增益、線性度和頻率響應(yīng)。借助專業(yè)軟件開發(fā)工具進(jìn)行仿真設(shè)計(jì),是現(xiàn)代集成電路設(shè)計(jì)流程中不可或缺的環(huán)節(jié)。

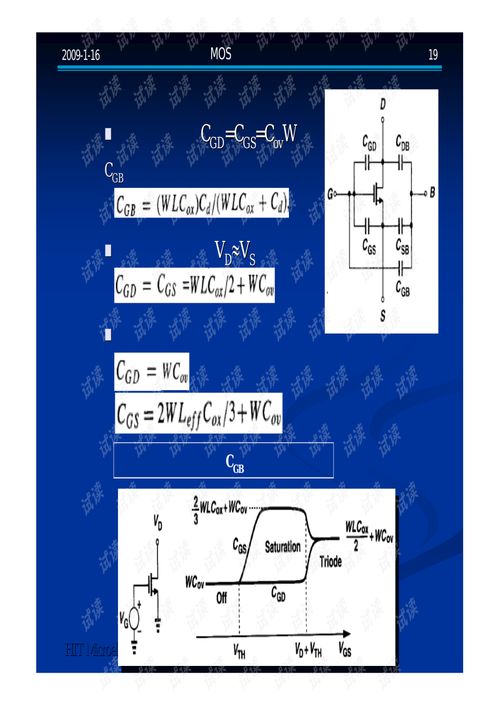

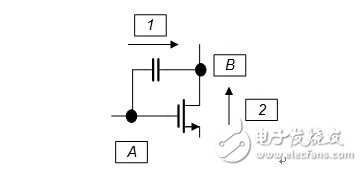

我們來探討MOS管的輸出電阻rout。rout定義為MOS晶體管在飽和區(qū)工作時(shí),漏極電流對(duì)漏極電壓的微小變化的抵抗能力,數(shù)學(xué)上表示為rout = ?Vds/?Id。高輸出電阻有利于提高放大器的電壓增益,因?yàn)樵鲆嫱ǔEcrout成正比。在實(shí)際設(shè)計(jì)中,rout受多個(gè)因素影響,包括溝道長度調(diào)制效應(yīng)和體效應(yīng)。

溝道長度L是MOS管的核心幾何參數(shù),它對(duì)rout有顯著影響。一般而言,隨著L的增加,rout也會(huì)增大。這是因?yàn)檩^長的溝道長度減少了溝道長度調(diào)制效應(yīng),導(dǎo)致漏極電流對(duì)漏極電壓的變化更不敏感。例如,在長溝道器件中,rout近似與L成正比,這有助于設(shè)計(jì)高增益放大器。增加L也會(huì)帶來缺點(diǎn),如降低晶體管的截止頻率和增加芯片面積,因此在設(shè)計(jì)過程中需要權(quán)衡性能與成本。

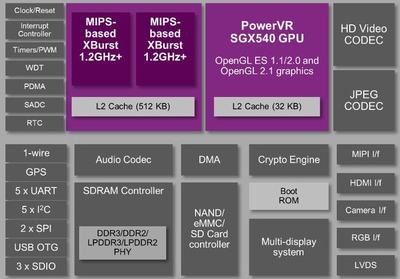

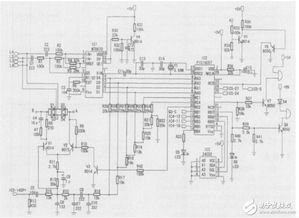

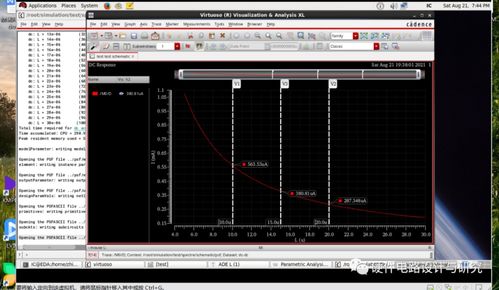

在集成電路仿真設(shè)計(jì)中,軟件開發(fā)工具如SPICE(例如HSPICE、LTspice或Cadence Virtuoso)扮演著關(guān)鍵角色。這些工具允許工程師通過參數(shù)掃描和優(yōu)化算法來模擬不同L值對(duì)rout的影響。例如,設(shè)計(jì)者可以設(shè)置L從最小值(如工藝允許的0.18μm)逐步增加到較大值(如1μm),并觀察rout的變化曲線。通過仿真,可以快速驗(yàn)證理論模型,避免實(shí)物原型的高成本。軟件還提供自動(dòng)優(yōu)化功能,幫助在滿足增益、功耗和面積約束下,選擇最優(yōu)的L值。

理解MOS管的rout與L的關(guān)系是模擬CMOS設(shè)計(jì)的基礎(chǔ),而軟件開發(fā)則提供了高效的設(shè)計(jì)和驗(yàn)證手段。隨著工藝節(jié)點(diǎn)的不斷縮小,精確控制這些參數(shù)變得尤為重要。結(jié)合機(jī)器學(xué)習(xí)的EDA工具可能進(jìn)一步優(yōu)化這一過程,推動(dòng)集成電路技術(shù)的持續(xù)創(chuàng)新。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.tpyd.com.cn/product/32.html

更新時(shí)間:2026-03-09 07:40:40