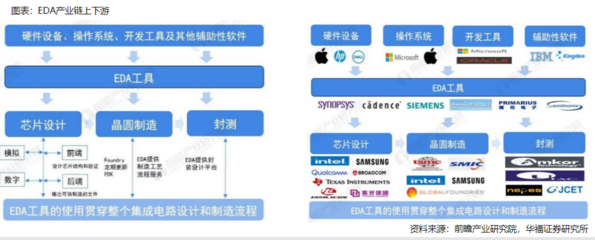

集成電路設(shè)計(jì)軟件概覽 電腦版與數(shù)字集成電路設(shè)計(jì)工具

集成電路設(shè)計(jì)軟件是現(xiàn)代電子工程中不可或缺的工具,用于設(shè)計(jì)、模擬和驗(yàn)證集成電路(IC)。這些軟件幫助工程師將復(fù)雜的電路設(shè)計(jì)轉(zhuǎn)化為實(shí)際的芯片布局。根據(jù)應(yīng)用領(lǐng)域,集成電路設(shè)計(jì)軟件可大致分為模擬、數(shù)字和混合信號(hào)設(shè)計(jì)工具。本文將重點(diǎn)介紹電腦版集成電路設(shè)計(jì)軟件,特別是數(shù)字集成電路設(shè)計(jì)軟件,并簡(jiǎn)要提及相關(guān)下載資源。

一、集成電路設(shè)計(jì)軟件的分類

集成電路設(shè)計(jì)軟件根據(jù)功能和應(yīng)用分為多個(gè)類別:

- 模擬集成電路設(shè)計(jì)軟件:專注于處理連續(xù)信號(hào),如音頻或射頻電路。常見工具包括 Cadence Virtuoso 和 Synopsys HSpice。

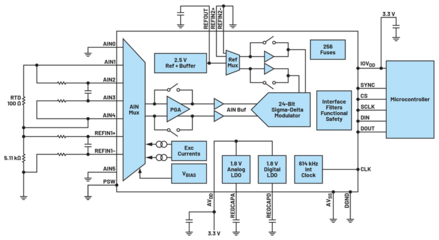

- 數(shù)字集成電路設(shè)計(jì)軟件:處理離散信號(hào),用于設(shè)計(jì)邏輯電路、處理器和存儲(chǔ)器等。這些工具通常支持硬件描述語言(如 Verilog 或 VHDL)。

- 混合信號(hào)設(shè)計(jì)軟件:結(jié)合模擬和數(shù)字功能,適用于復(fù)雜系統(tǒng)芯片(SoC)設(shè)計(jì)。

二、電腦版集成電路設(shè)計(jì)軟件

電腦版集成電路設(shè)計(jì)軟件指在個(gè)人計(jì)算機(jī)或工作站上運(yùn)行的桌面應(yīng)用程序。這些軟件提供圖形用戶界面(GUI),便于工程師進(jìn)行設(shè)計(jì)、仿真和優(yōu)化。以下是一些主流工具:

1. Cadence Virtuoso:廣泛用于模擬和混合信號(hào)設(shè)計(jì),提供強(qiáng)大的布局和仿真功能。

2. Synopsys Design Compiler:專注于數(shù)字邏輯綜合,幫助將高級(jí)代碼轉(zhuǎn)換為門級(jí)網(wǎng)表。

3. Mentor Graphics (現(xiàn)為 Siemens EDA) 的 Tanner Tools:適合中小型項(xiàng)目,支持模擬和數(shù)字設(shè)計(jì)。

4. Xilinx Vivado:主要用于 FPGA 設(shè)計(jì),但也支持?jǐn)?shù)字集成電路開發(fā)。

這些軟件通常需要高性能計(jì)算機(jī),以處理大規(guī)模設(shè)計(jì)任務(wù)。

三、數(shù)字集成電路設(shè)計(jì)軟件

數(shù)字集成電路設(shè)計(jì)軟件專門針對(duì)數(shù)字電路,例如微處理器、DSP 和 ASIC。核心工具包括:

- 邏輯仿真器:如 ModelSim 和 VCS,用于驗(yàn)證設(shè)計(jì)功能。

- 綜合工具:如 Synopsys Design Compiler,將硬件描述語言轉(zhuǎn)換為邏輯門。

- 布局與布線工具:如 Cadence Innovus,負(fù)責(zé)物理設(shè)計(jì)。

- 驗(yàn)證工具:確保設(shè)計(jì)符合規(guī)格,例如使用 Formal Verification 工具。

這些軟件支持從 RTL(寄存器傳輸級(jí))到 GDSII(芯片制造文件)的完整流程,是數(shù)字芯片開發(fā)的核心。

四、下載資源與注意事項(xiàng)

用戶常通過在線平臺(tái)如 9553 下載站獲取軟件試用版或免費(fèi)工具。請(qǐng)注意:

- 合法性:許多專業(yè)軟件(如 Cadence 或 Synopsys 產(chǎn)品)是商業(yè)軟件,需要購(gòu)買許可證。免費(fèi)版本可能功能受限。

- 安全風(fēng)險(xiǎn):從非官方來源下載可能包含惡意軟件,建議優(yōu)先訪問官方網(wǎng)站或可信渠道。

- 學(xué)習(xí)資源:對(duì)于初學(xué)者,開源工具如 Magic VLSI 或商業(yè)軟件的學(xué)術(shù)版是不錯(cuò)的選擇。

五、廣告設(shè)計(jì)與集成電路軟件的關(guān)聯(lián)

雖然廣告設(shè)計(jì)通常指視覺傳達(dá)領(lǐng)域,但與集成電路設(shè)計(jì)軟件存在間接聯(lián)系。例如,在電子產(chǎn)品營(yíng)銷中,廣告可能需要展示芯片設(shè)計(jì)過程,使用這些軟件的渲染圖或模擬結(jié)果。集成電路設(shè)計(jì)軟件本身也涉及用戶界面設(shè)計(jì),這需要一定的廣告設(shè)計(jì)原則來提升用戶體驗(yàn)。

集成電路設(shè)計(jì)軟件是電子行業(yè)的關(guān)鍵工具,電腦版軟件如 Cadence 和 Synopsys 系列在數(shù)字設(shè)計(jì)領(lǐng)域占據(jù)主導(dǎo)地位。用戶應(yīng)通過正規(guī)渠道獲取軟件,并結(jié)合實(shí)際需求選擇合適工具。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.tpyd.com.cn/product/17.html

更新時(shí)間:2026-03-07 18:34:56